See CMP-50X for custom solution!

### **FEATURES**

- Includes critical structures such as vias, crosstalk aggressors, impedance analysis, ground voids, meshing, loss, and material ID for complete EDA benchmarking

- Allegro layout (.brd or OBD++) available for easy 3D EM import (NDA required)

- Measured S-parameters files included for each structure, tested for quality, includes DC point for immediate time domain analysis

- Material extraction method, including surface roughness

- Model libraries available for use in

- o HFSS

- Simbeor THz

- TDNA-VNA analysis structures

- TDR resolvers for ultra-fast TDR (10 psec. and 28 psec. rise times) for EDA time domain calibration

- HFSS set-up, and material ID (X-Y and Zaxis, Tensor-based) web-based training

### **APPLICATIONS**

- Establish 50GHz High-Confidence Design

- Learn how to design 1<sup>st</sup> spin designs to 50GHz and achieve IEEE P370 TG1 signal integrity rated quality

- Benchmark simulations, test meshing, port boundaries, solver approach

- Improve signal integrity methodology of common structures (voids, vias, breakouts, cavities, etc.)

- De-embedding validation and measurement validation

- VNA, TDNA measurement validation to 50 GHz, 8 psec. resolution

For custom solutions based on customer stackup refer to CMP-50X

CMP-50 Standard Product. For custom solutions based on customer stack-up refer to CMP-50X

## **Program Contents:**

- CMP-50 Platform, assembled and 100% TDR QA tested, with custom stands

- Cross-section for that platform, use as-fabricated geometries

- Measured S-parameters, pre-tested for quality (passivity/causality and resampled for time domain simulations)

- PCB layout design files (NDA required)

- EDA Library including Loss Models, including Industry First accurate surface roughness models

- Comprehensive training for 3D EM analysis correspondence, material ID in X-Y and Z axis in HFSS

The CMP-50 Channel Modeling Platform represents a powerful next generation tool for development of high-speed 50 GHz systems. The standard product is also used as a template for a custom modeling solution which utilizes a customer specific stack-up and fabricator. The primary target application for this product is 3D-EM solver analysis modeling versus time and frequency domain measurement methodology. All structures include de-embedding to isolate the device-under-test (DUT) using Symmetrical De-embedding such as Automatic Fixture Removal (AFR, both 1X and 2X) or Measure Based Model (MBM) using ADS.

## **SPECIFICATIONS**

#### Table 1 – CMP-50 platform specifications

| PC board material | Isola I-Tera MT40                                                                                                     |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| Connectors        | 2.4mm vertical launch female (VLF), compression mount, replaceable. All connector launches are NIST traceable tested. |

| Dimensions        | 16" x 16" without stands                                                                                              |

#### Table 2 – Test Structures Included by category

| Simple transmission structures for material Identification and simple transmission modeling | SingleOended and differential traces of different lengths for<br>General Modal material ID determination                |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Pathological                                                                                | Untuned connector launch vias and test vias, crosstalk generators, diff pair with adjacent plane cutout                 |

| Meshing Challenges                                                                          | Graduated Co-planar - Challenges 3D EM mesh approach                                                                    |

| Time Domain Challenges                                                                      | Untuned vias, Beatty standards, Thru with whiskers (TDR resolvers for ultra-fast TDR, 10 psec. and 28 psec. rise times) |

| Z Axis Challenges                                                                           | Untuned vias, differential pair with adjacent plane cutout                                                              |

| VNA Calibration                                                                             | Short, Open, Load, Thru, 1X THRU, 2X THRU                                                                               |

| Generating circuit resonance                                                                | Balanced resonator, ring resonators, stub resonators, anisotropic resonator                                             |

| Intersymbol Interference                                                                    | Ultra-long differential traces, 16" and 32"                                                                             |

For details and to request a quote us at sales@wildrivertech.com. Contact Al Neves at <a href="mailto:al@wildrivertech.com">al@wildrivertech.com</a> for a 45minute technical presentation called "Extreme Signal Integrity to 50GHz" that outlines the WRT signal integrity program for:

- What is IEEE P370 TG1, how to achieve good SI in one spin

- Material ID methods in all X-Y and Z direction in HFSS

- Setting up your EDA tool for stellar simulation to measurement

- Making good measurements, S-parameter quality work flows

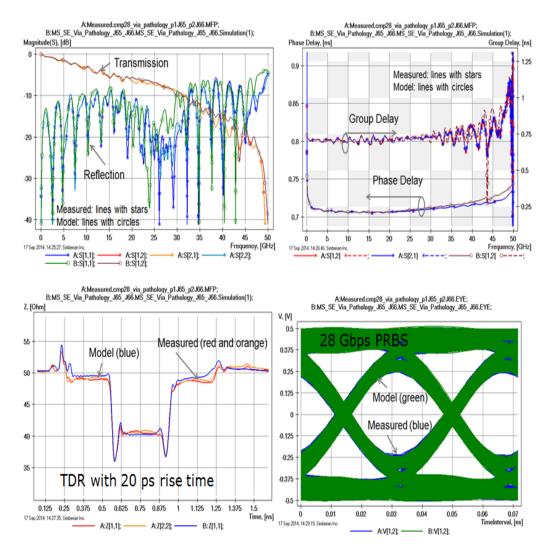

### EDA KIT AVAILABLE

An EDA is a zipped simulation environment, which includes the board layout, simulation set up and results, and correspondence to measurements for structures on the CMP-50 platform. An example is shown below of simulation to measurement of a pathological structure on the CMP-50. Several EDA kits use a full path approach and others use both de-embedded and full path. Full path includes models of the connector launches. Contact WRT for more information on EDA kits for CMP-50.

## What's Included

The price for the CMP-50 is expected to be around \$16.9K with 2.4mm connector installed. For this price you get:

- Fully assembled system, 100% NIST traceable TDR tested, report included

- S-parameter library, measured, tested for quality, includes DC point

- COM metrics

- · Web-based product training with WRT Applications Engineer, scheduled at customers convenience

## **Ordering Instructions**

| Part Number | Model         | Description                                                             |

|-------------|---------------|-------------------------------------------------------------------------|

| 916-0001-00 | CMP-50-1.85mm | Advanced Channel Modeling Platform assembled with 1.85mm VLF connectors |

| 916-0002-00 | CMP-50-2.4mm  | Advanced Channel Modeling Platform assembled with 2.4mm VLF connectors  |

### Accessories

| Part Number | Model        | Description                                                                                                                                                                                                                                                 |

|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 906-0002-00 | Cable Bundle | Four cable pair bundle, blue DXM086 flexible coaxial cable assemblies with 2.4mm compatible male connectors on both ends. Specification: 16dB return loss or better through 50GHz, 1ps or less skew matched cable pairs. Lengths: 2 x 42", 1 x 36", 1 x 24" |

| 907-0016-00 | Case         | Pelican case with custom cut foam for 16 sq in WRT platforms                                                                                                                                                                                                |