Achieving high levels of accuracy between predicted and actual performance is a critical goal for any team doing advanced chip design. Getting what you expect from manufacturing can cut design time, improve cost margins, decrease time to market and generally improve overall success for the project. Achieving this goal is not easy. Many design and calibration steps must be executed flawlessly. There was a panel devoted to this topic at the recent DesignCon in Santa Clara, CA. Experts looked at the problem from several different perspectives, including accuracy and calibration, design methodology and putting results to work in real products. Read on to learn more – can correlation between simulation and measurement be achieved for advanced designs?

The Panel

The DesignCon panel was entitled, Extreme Confidence Simulation for 400-800G Signal Integrity Design. The event was organized by Wild River Technology, a supplier of products and services for advanced signal integrity design.

Panelists spanned targeted support for advanced signal integrity designs, overall design methodology and the development of products that require advanced signal integrity. Here is a summary of the team that presented – an impressive group with substantial credentials.

Cathy Liu, Distinguished Engineer, Broadcom

Cathy Ye Liu currently heads up Broadcom SerDes architecture and modeling group. Since 2002, she has been working on high-speed transceiver solutions. Previously she has developed read channel and mobile digital TV receiver solutions.

![Cathy_Liu[1]](https://wildrivertech.com/wp-content/uploads/2024/04/Cathy_Liu1.png)

Gary Lytle, Product Management Director, Cadence

Gary leads product strategy, positioning, sales enablement and demand generation for Cadence electromagnetic simulation technologies. He has held may positions in the RF and Simulation industry, including Technical Director with ANSYS, Inc, Lead Antenna Design Engineer with Dielectric Communications, Combat Systems Engineer with General Dynamics and Engineering Manager with Amphenol.

![Gary_Lytle[1]](https://wildrivertech.com/wp-content/uploads/2024/04/Gary_Lytle1.png)

Scott McMorrow, Strategic Technologist, Samtec

Scott currently serves as a Strategic Technologist for Samtec, Inc. As a consultant for many years, Scott has helped many companies develop high performance products, while training signal integrity engineers. He is a frequent author and spokesperson for Samtec.

Al Neves, Founder & Chief Technology Officer, Wild River Technology

Al has over 39 years of experience in the design and application development of semiconductor products, capital equipment design focused on jitter and signal integrity analysis. He has successfully been involved with numerous business developments and startup activity for the last 17 years. Al focuses on measure-based model development, ultra-high signal integrity serial link characterization test fixtures, high-speed test fixture design, and platforms for material identification and measurement-simulation to 110 GHz.

Jim Weaver, Senior Design & Signal Integrity Engineer, Arista Networks

Jim is responsible for design and analysis of large switches for cloud computing and high bit rate serial links. Jim has over 40 years of experience in system design, including 20 years of signal integrity experience, and is heavily involved with IEEE802.3dj electrical specification work.

Todd Westerhoff, High-Speed Design Product Marketing at Siemens EDA

Todd Westerhoff moderated the panel. He has over 42 years of experience in electronic system modeling and simulation, including 25 years of signal integrity experience. Prior to joining Siemens EDA, he held senior technical and management positions at SiSoft, Cisco and Cadence. He also worked as an independent signal integrity consultant developing analysis methodologies for major systems and IC manufacturers.

The focus of the panel was summarized this way:

What’s the point in running detailed simulations if the PCB test vehicle you fabricate and assemble performs differently than you had predicted? This panel will discuss issues associated with achieving tight and repeatable correlation between simulation and measurement for structures such as vias, connector launches, transmission lines, etc. and the channels that contain them.

This correlation allows us to perform what we call “Extreme Confidence Simulation”. A wide set of simulation topics will be addressed that are focused on the epic signal integrity challenges presented by 400-800G communication.

Key Takeaways

Broadcom

Cathy Liu explained that Broadcom has demonstrated and shipped multiple 100G SerDes solutions across the industry. The results were achieved with a variety of process nodes (7nm, 5nm and 3nm). Power efficiency targets varied by application and different architectural approaches such as analog SerDes and DSP SerDes were used. The key point is that one approach will not be power optimal for all applications, you have to be ready to find the right blend of architecture, process and specifications.

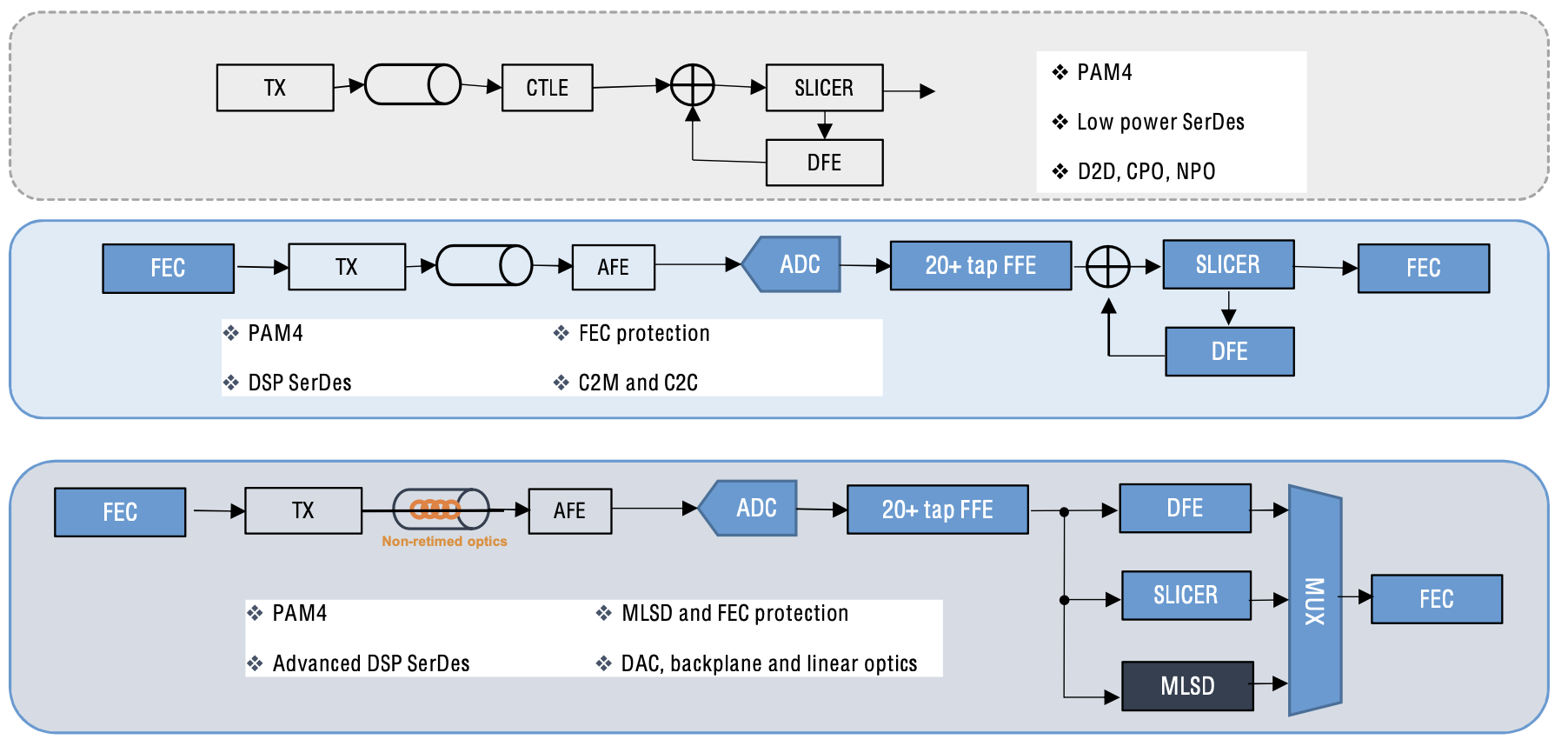

She went on to describe Broadcom’s experiences using various approaches, the results achieved and the places where careful attention to correlation and accuracy was needed. This is not a simple process and deep technical understanding is critical to success. The figure below shows some of the approaches discussed.

Sample of Broadcom Architectures

Cadence

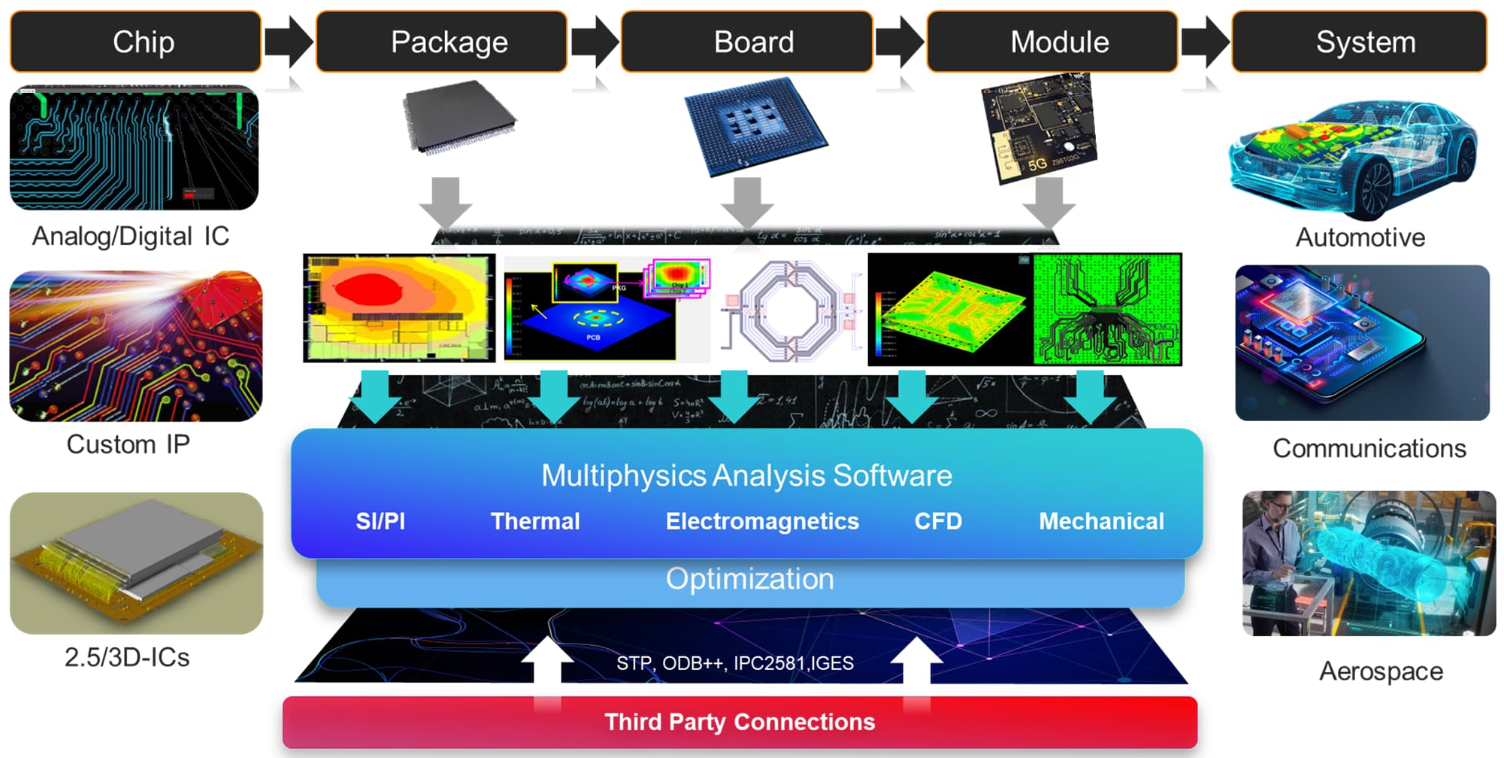

Gary Lytle took a broad view of the development process. This included material properties, models and model validation, simulation vs. real world results, stack-up creation to EDA design, tool interoperability, training, and flexibility/scalability. The figure below illustrates the complex relationships involved.

Design Flow Complexity (Cadence)

Challenges include data transfer logistics model sharing, and verification. Using an “over-the-wall” mentality won’t yield the best results.

Component models are key, and some attributes to be considered include:

- Encryption models

- Quality, shareability, assembly, validation, open standard

- Protection of vendor IP

- Healing

- As-mated or as-built

- Simulated vs. measured

- Testing

Gary summarized by pointing out that EDA is a solution, not a tool. Success requires teams to break down silos and enable methodologies that are metric driven and not subjective.

Samtec

Scott McMorrow provided his views and experience, beginning with the observation that, in order to correlate measurements to simulation, it is necessary to understand the limits of the methods. We assume our simulations are correct given correct modeling inputs. Further, we assume our measurements are correct given the best measurement methods. But are they?

Scott pointed out that there is a statistical probability of error in both the simulations and the measurements that has nothing to do with correct modeling of materials. Therefore, we need to understand these to improve our measurement to model correlation.

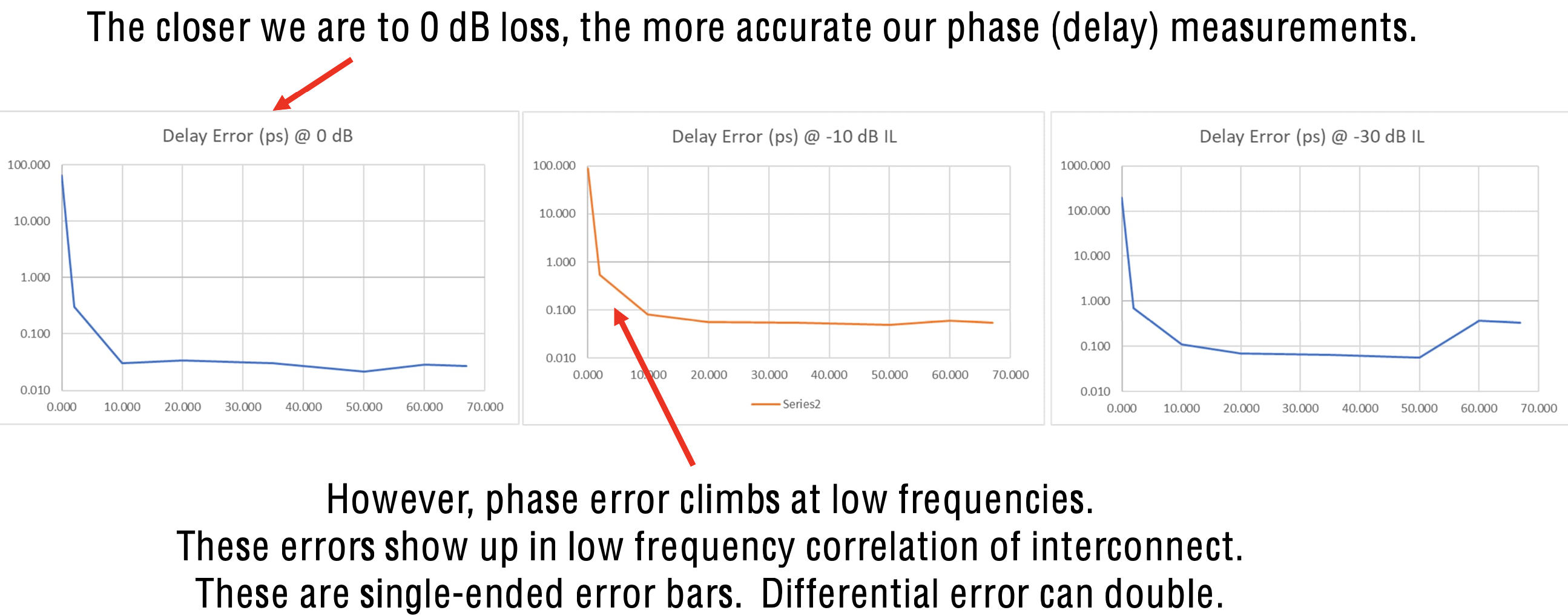

Scott then dove into significant detail to discuss HFSS simulation maximum delta S criteria, HFSS simulation convergence criteria, high frequency phase accuracy, transmission uncertainty, Mcal insertion loss error, and Mcal delay error. Examples of MCAL delay error are shown below.

MCAL Delay Error (Samtec)

Scott concluded his talk with a summary of what’s needed to understand the limits of measurement. For simulation modeling, understanding the convergence controls to achieve the necessarily level of correlation is mandatory.

A final comment from Scott: Separate correlation to individual structures so that accuracy can be preserved in both simulation and measurement.

Arista Networks

Jim Weaver itemized the many challenges faced by advanced signal integrity design. These include:

IC package loss, already a large fraction of the loss budget that can be 30%+ for 200Gbps (53.125GHz). In large switches, over half the chip-chip budget is package loss. This must be accounted for in initial system design. Jim pointed out that early and ongoing vendor data on package losses and crosstalk are crucial.

He also discussed PCB loss. Trace losses per unit length are high at 26GHz and very high at 53GHz. Connectors and cables were also discussed. Larger connector losses are significant, and vendors must supply electrical model for channel simulations, 3D models for footprint design, and cable models. These models must reflect reality, for example, take account of temperature effects.

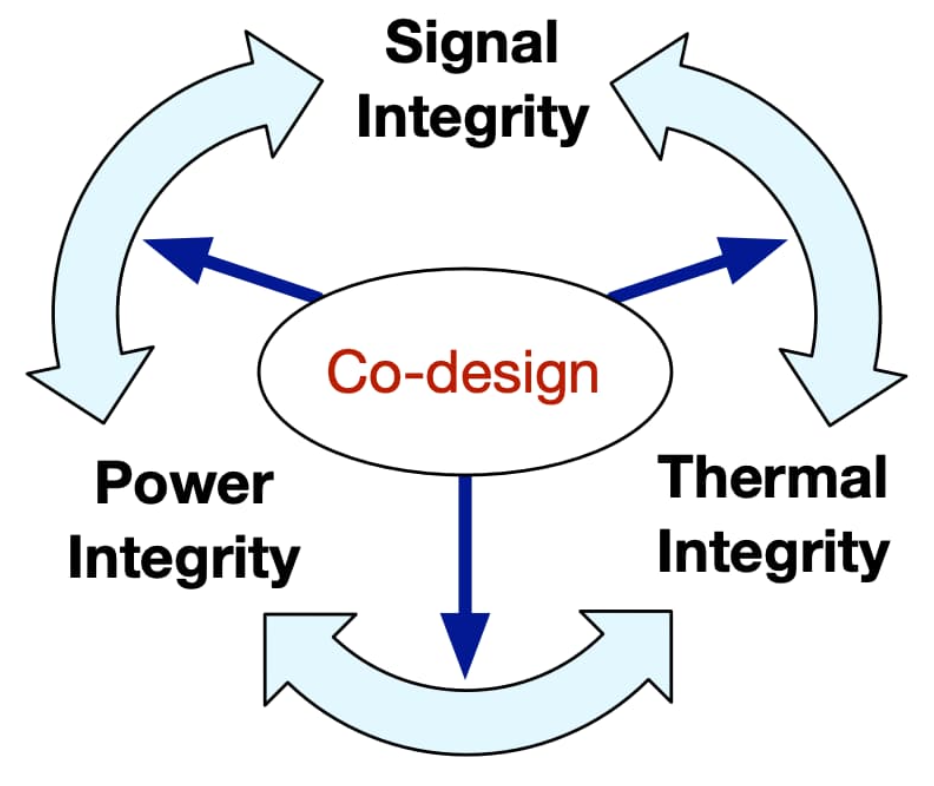

He also discussed return (i.e. reflection) losses and crosstalk. PCB routing density challenges were also discussed, as was power dissipation and power delivery challenges. Forced air, immersion, and hybrid cooling systems were explored. The key point of all this discussion was that signal, power, and thermal designs interact — co-design is now a must and requisite data from vendor partners is critical as illustrated in the figure below.

Co-Design is a Must (Arista Networks)

Wild River Technology

Al Neves took a direct approach to the topic, pointing out that EDA tools are not standards. “There is nothing “golden” about them (sorry). Believing EDA tools are standards can corrupt the path to high-speed design confidence.” He went on to explain that the path to simulation-to-measurement confidence is a hard road that takes a lot of work and it’s uncompromising.

The hard work is EDA calibration/benchmarking and building systematic approaches using advanced test fixtures (material ID, verification of models, etc.) The bottom line is that all EDA tools have issues, and it is our job to identify and work around them.

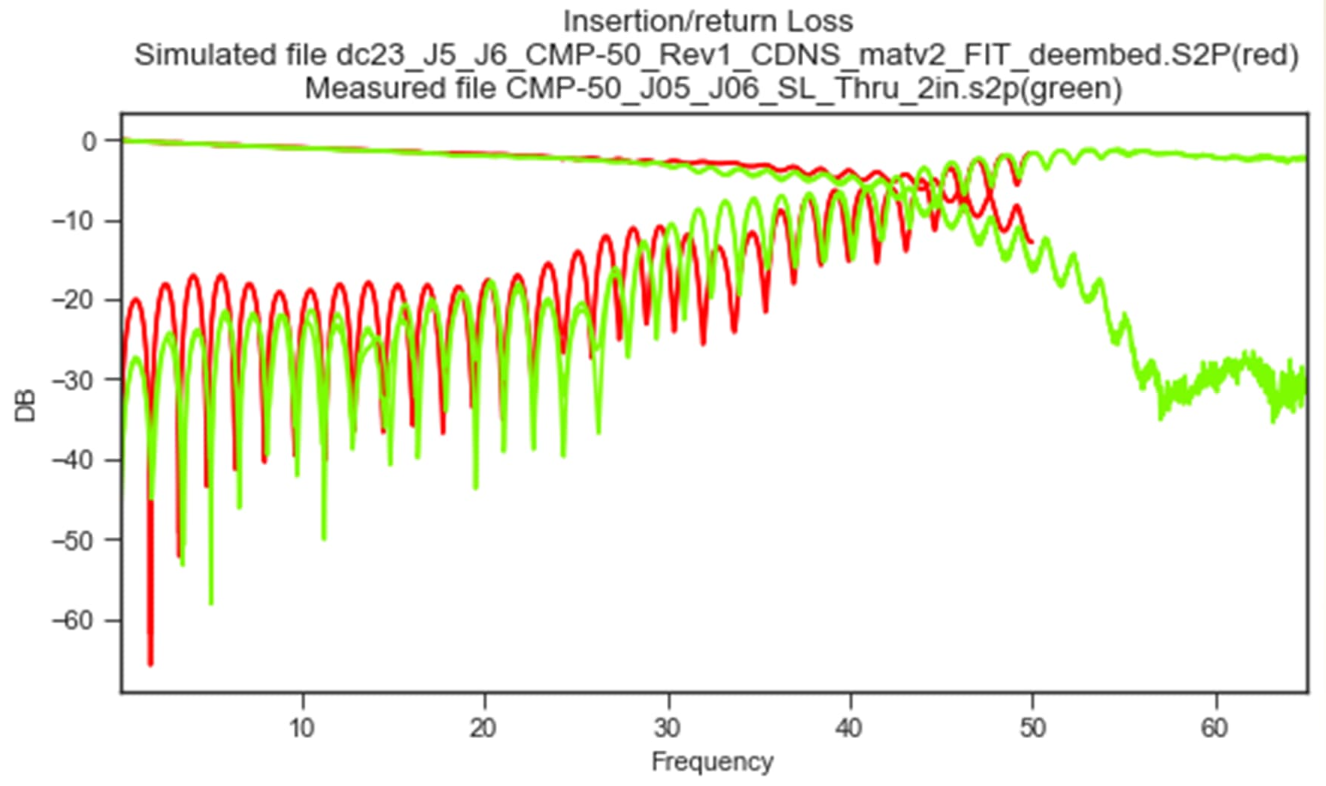

Al then spent some time on the importance of calibration and metrics. He explained that better calibration is required for simulation-measurement. For example, sliding load cal performance is required for good sim-measure correspondence. He felt the industry was over reliant on easy-to-use ECAL and the industry has neglected good mechanical calibrations. The figure below illustrates an error plot of simulated vs. measured insertion/return loss. This work was a collaboration with Cadence.

Insertion_Return Loss Error Plot (Wild River Technology)

Al coined the term EDA Metrics Matter. His concluding points were:

- Mindset matters – you cannot ignore Maxwell

- The world of >70GHz is not in good shape for signal integrity

- Metrics will be very useful

Industry Collaboration – Cadence and Wild River Technology

The challenges discussed during this panel require industry-level collaboration. An example of this collaboration is the work being done between Cadence and Wild River Technology (WRT).

Cadence is using WRT’s CMP-50 Advanced Channel Modeling Platform for benchmarking its Clarity 3D Solver against the associated EM correlation across multiple workflows and is inclusive of WRT’s 400-800 gigabit Ethernet simulation solution for designing critical interconnects for PCBs, IC packages and systems on IC (SoIC).

As part of this collaboration, Cadence is using a host of advanced correspondence tools (S-parameters) and complementing time-domain transformed (TDR) impedance data along with proprietary tools being developed that corresponds S-parameters as vectors, such as the Modified Hausdorff Distance metrics and causal material models.

Industry Collaboration – Samtec and Wild River Technology

WRT is using the very accurate 3D EM models supplied by Samtec to achieve high confidence launch design. As part of this program, we are using WRT’s latest channel modeling platform with Samtec’s 1.85mm Precision RF 50 ohm connector launch.

Capabilities of this connector include:

- Performance to 65 GHz

- Vertical or edge launch, solderless compression

- Stripline or microstrip/CPW transmission

- Alignment features (vertical): with the addition of fiducials on the PCB any visual misalignment is eliminated, ensuring peak connector performance

- Ideal for high-performance test applications

- Cable connectors, compatible with industry standard cables, also available

You can review a comprehensive description of the importance of alignment on connector performance and VSWR with some very useful return loss/VSWR plots in this article.

This technology allows us to demonstrate complete electrical transparency with no detectable TDR bump. Our collaboration with Cadence and Samtec is helping to achieve Extreme Signal Integrity.

Summary, and Next Steps

There were common themes in this panel discussion. Breaking down silos and collaborating between teams and with ecosystem partners is required for success. Understanding how to calibrate results and factor in all sources of errors, including an understanding the materials being used is also important.

Wild River Technology is at the epicenter of a lot of these requirements. You can explore the extreme signal integrity products and services offered by the company here. You can also reach out to discuss your specific needs here. With the right partner and the right mindset, simulation accuracy for advanced designs can be achieved.